AD9525时钟发生器参数介绍及中文PDF下载

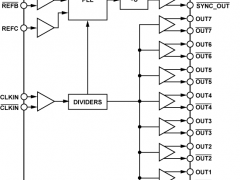

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。AD9525提供低功耗、多路输出时钟分配功能,具有低抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO或VCXO使用。VCO输入和八个LVPECL输出最高工作频率为3.6 GHz。所有输出共用一个分频器,分…

2020-04-27 14:05:58

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。AD9525提供低功耗、多路输出时钟分配功能,具有低抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO或VCXO使用。VCO输入和八个LVPECL输出最高工作频率为3.6 GHz。所有输出共用一个分频器,分…

2020-04-27 14:05:58

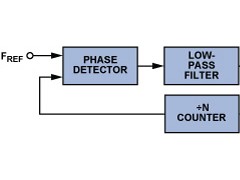

本文探讨了当前具有高电压 VCO 的 PLL 设计,包括典型架构的利弊以及高电压 VCO 的替代选项。

2020-04-26 15:12:05