什么是上拉电阻器?

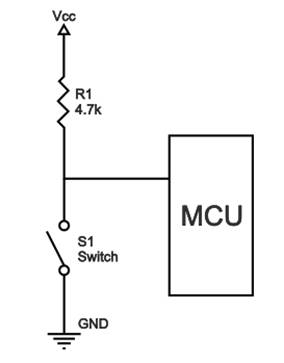

上拉电阻是逻辑电路中使用的电阻,用于确保引脚在所有条件下具有明确定义的逻辑电平。提醒一下,数字逻辑电路有三种逻辑状态:高、低和浮动(或高阻抗)。当引脚未被拉至高或低逻辑电平,而是保持“浮动”状态时,就会发生高阻抗状态。一个很好的例子是微控制器的未连接输入引脚。它既不处于高逻辑状态,也不处于逻辑低电平状态,微控制器可能会不可预测地将输入值解释为逻辑高电平或逻辑低电平。上拉电阻用于通过将值拉至逻辑高电平状态来解决微控制器的困境,如下图所示。

上拉电阻上拉电阻电路

如果没有上拉电阻,MCU的输入将在开关打开时处于浮动状态,而只有在开关闭合时才会下拉至逻辑低电平。

上拉电阻器不是一种特殊的电阻器;它们只是连接在电源(通常为+5 V、+3.3 V或+2.5 V)和相应引脚之间的固定值电阻,从而在没有驱动信号的情况下定义输入或输出电压。典型的上拉电阻值为4.7 kΩ,但可能因应用而异,本文稍后将对此进行讨论。

上拉电阻器定义

上拉电阻器是用于确保在没有输入信号的情况下将导线拉至高逻辑电平的电阻器。

什么是下拉电阻器?

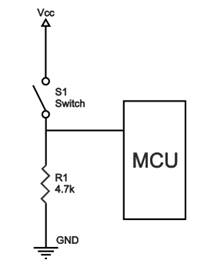

下拉电阻的工作方式与上拉电阻相同,只是它们将引脚拉至逻辑低值。它们连接在接地和设备上的相应引脚之间。下图显示了数字电路中下拉电阻的示例。

下拉电阻器下拉电阻

在该图中,电源电压和微控制器引脚之间连接了一个按钮开关。在此类电路中,当开关闭合时,微控制器输入处于逻辑高电平,但当开关开路时,下拉电阻将输入电压拉低至地电位(逻辑零值),从而防止输入端出现未定义状态。下拉电阻的电阻必须大于逻辑电路的阻抗,否则它可能会将电压拉低太多,并且引脚上的输入电压将保持在恒定的逻辑低值,而不管开关位置如何。

上拉和下拉电阻值

上拉(或下拉)电阻的适当值受两个因素的限制。个因素是功耗。如果电阻值太低,则高电流将流过上拉电阻器,使器件发热,并在开关闭合时消耗不必要的功率。这种情况称为强上拉,当需要低功耗时,可以避免这种情况。第二个因素是开关断路时的引脚电压。如果上拉电阻值过高,再加上输入引脚的漏电流大,开关断路时输入电压会变得不足。这种情况称为弱引体向上。上拉电阻的实际值取决于输入引脚的阻抗,而输入引脚的阻抗与引脚的漏电流密切相关。

经验法则是使用至少比输入引脚阻抗值小 10 倍的电阻。在工作电压为5 V的双极性逻辑系列中,典型的上拉电阻值为1-5 kΩ。对于开关和电阻式传感器应用,典型的上拉电阻值为1-10 kΩ。如有疑问,使用开关时的良好起点是 4.7 kΩ。一些数字电路(如CMOS系列)具有较小的输入漏电流,允许更高的电阻值,从10 kΩ到1 MΩ不等。使用较大电阻值时的缺点是输入引脚对电压变化的响应缓慢。这是上拉电阻与开关节点上的总引脚和导线电容耦合的结果,从而形成RC电路。R和C的乘积越大,电容充放电所需的时间就越长,因此电路的速度就越慢。在高速电路中,较大的上拉电阻有时会限制引脚可靠地改变状态的速度。

上拉和下拉电阻的典型应用

上拉和下拉电阻通常用于将开关或其他输入与微控制器或其他数字门连接时。大多数微控制器都内置了可编程上拉和/或下拉电阻器,因此需要的外部元件更少。可以直接将开关与这些微控制器连接。上拉电阻通常比下拉电阻更常用,尽管某些微控制器系列同时提供上拉和下拉电阻。

它们通常用于在传感器输出电压信号进行模数转换之前,为电阻传感器提供受控电流。

另一个应用是 I2C 协议总线,其中上拉电阻用于使单个引脚充当输入或输出。当未连接到总线时,引脚在高阻抗状态下浮动。

输出端还使用下拉电阻器来提供已知的输出阻抗。

客服微信

客服微信 查ic网订阅号

查ic网订阅号