AD9528相关信息来自ADI官网,具体参数以官网公布为准,AD9528供应信息可在查IC网搜索相关供应商。

产品详情

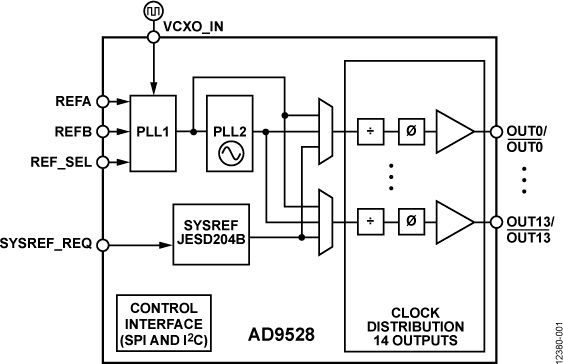

AD9528是一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级PLL (PLL2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部VCXO提供PLL2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内VCO的调谐频率范围为3.450 GHz至4.025 GHz。集成的SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,以便对齐多个器件的时间。

AD9528产生最高频率为1.25 GHz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1 GHz的八路输出。每一路输出均可配置为直接从PLL1、PLL2或内部SYSREF发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。AD9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或SYSREF信号的分配。启动时,AD9528直接向输出12和输出13发送VCXO信号,用作启动就绪时钟。

注意在整篇数据手册中,双功能引脚名称通过适用的相关功能来引用。

应用

- 高性能无线收发器

- LTE和多载波GSM基站

- 无线和宽带基础设施

- 医疗仪器

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟;支持JESD204B

- 低抖动、低相位噪声时钟分配

- 自动测试设备(ATE)和高性能仪器仪表

优势和特点

- 14路输出,可配置为HSTL或LVDS

- 最大输出频率

- 6路输出高达1.25 GHz

- 8路输出高达1 GHz

- 取决于压控晶体振荡器

- (VCXO)频率精度(启动频率精度:<±100 ppm)

- 每路输出均提供专用的8位分频器

- 粗调延迟: 63个步长为RF VCO分频器输出频率一半的步进,不受抖动影响

- 微调延迟: 15个步进,分辨率为31 ps

- 典型输出间偏斜: 20 ps

- 针对奇数分频器设置提供占空比校正

- 输出12和输出13,上电时VCXO输出

- 绝对输出抖动: <160 fS(122.88 MHz时)

12 kHz至20 MHz积分范围 - 数字锁频检测

AD9528电路图

AD9528中文PDF下载地址

AD9528下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/ad9528.pdf

免责声明:

以上相关内容来自互联网公开信息分享;如涉及内容、版权、图片等问题,请联系我们。会第一时间删除!

客服微信

客服微信 查ic网订阅号

查ic网订阅号