AD9572相关信息来自ADI官网,具体参数以官网公布为准,AD9572供应信息可在查IC网搜索相关供应商。

产品详情

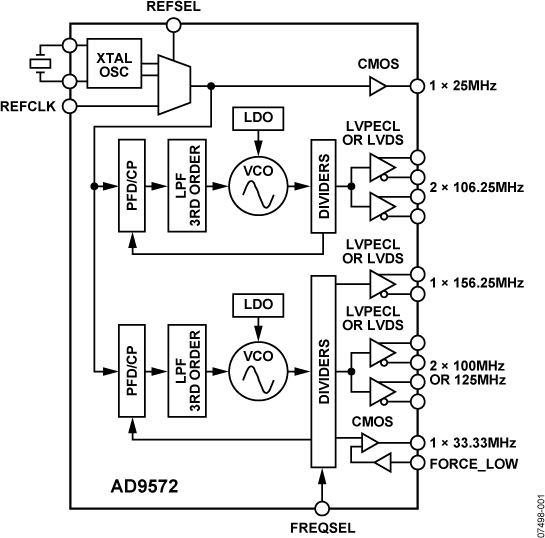

AD9572是一款多输出时钟发生器,具有两个片内PLL内核,针对包括以太网接口的光纤通道线路卡应用进行了优化。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现网络的最高性能。这款器件也适合相位噪声和抖动要求严格的其它应用。PLL部分由低噪声鉴频鉴相器(PFD)、精密电荷泵(CP)、低相位噪声压控振荡器(VCO)、预编程的反馈分频器和输出分频器组成。通过将一个外部晶振或参考时钟连接到REFCLK引脚,可以将最高156.25 MHz的频率锁定至输入参考。每个输出分频比和反馈分频比针对所要求的输出速率进行预编程。

第二个PLL也用作整数N分频频率合成器,并驱动两个LVPECL或LVDS输出缓冲器以支持106.25 MHz频率。无需外部环路滤波器,从而节省宝贵的设计时间和电路板空间。

AD9572提供40引脚6 mm × 6 mm、LFCSP封装,可以采用3.3 V单电源供电。温度范围为−40°C至+85°C。

应用优势和特点

|

|

AD9572电路图

AD9572中文PDF下载地址

AD9572下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD9572.pdf

客服微信

客服微信 查ic网订阅号

查ic网订阅号