ADF4196相关信息来自ADI官网,具体参数以官网公布为准,ADF4196供应信息可在查IC网搜索相关供应商。

产品详情

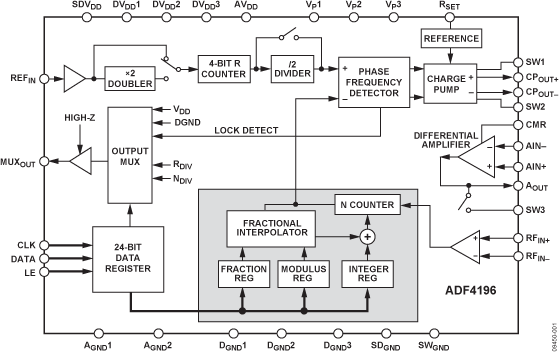

ADF4196频率合成器可以用来在无线接收机和发射机的上变频和下变频部分实现本振(LO),其结构专门设计用来满足基站的GSM/EDGE锁定时间要求,其快速建立功能则使ADF4196非常适合脉冲多普勒雷达应用。ADF4196由低噪声数字鉴频鉴相器(PFD)和精密差分电荷泵组成。还有一个差分放大器,用来将电荷泵的差分输出转换为外部电压控制振荡器(VCO)的单端电压。Σ-Δ型小数插值器与N分频器一起使用,能够实现可编程模数小数N分频。此外,4位参考(R)分频器和片内倍频器允许PFD输入端的参考信号(REFIN)频率为可选值。

如果频率合成器与外部环路滤波器和VCO一起使用,则可以实现完整的锁相环(PLL)。开关结构确保PLL能在GSM时隙保护期间内建立,而无需第二PLL及相关的隔离开关。与以前的乒乓式GSM PLL结构相比,这种结构能节省成本,降低复杂度,减小PCB面积,并减少屏蔽和特性测试工作。

应用

- GSM/EDGE基站

- PHS基站

- 脉冲多普勒雷达

- 仪器仪表和测试设备

- 波束形成/相控阵系统

优势和特点

- 快速建立小数N

分频PLL结构 - 单个PLL可取代乒乓式频率合成器

- 在5 μs内完成整个GSM频段上的跳频,相位建立时间低于20 &mICro;s

- 相位误差:1度rms

(4 GHz RF输出) - 数字可编程输出相位

ADF4196电路图

ADF4196中文PDF下载地址

ADF4196下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/ADF4196.pdf

免责声明:

以上相关内容来自互联网公开信息分享;如涉及内容、版权、图片等问题,请联系我们。会第一时间删除!

客服微信

客服微信 查ic网订阅号

查ic网订阅号