在许多控制系统的核心区域,数模转换器 (DAC) 在决定系统的性能和精度方面起着非常关键的作用。本文将介绍两款新的精密 16 位 DAC,并对通过缓冲高速互补电流输出 DAC 的输出以实现变压器同等性能的创意进行讨论。

片内系统基准电压源改善了精度

在恶劣环境下运行的电子系统可能必须在忍受极端温度的同时保持出色的精度和稳定性。此类系统往往需要多个分辨率高达 16 位的数模拟转换器。DAC 输出电压的精度最终取决于其基准电压的精度。为了在各种温度下实现这种水平的性能,通常会使用单独的精密基准电压源。然而,现在推出了包含低漂移基准电压源的全新精密四通道 DAC 系列,它的性能足够好,可以作为系统基准电压源。

基准电压源应在各种不同的负载、电源变化和温度条件下保持恒定的电压。不幸的是,高性能的独立基准电压源往往体积较大、成本昂贵且功耗高 — 而片内基准电压源往往性能不佳。

直到现在,当系统设计师面临是将精密的 DAC 与外部基准电压源配对,还是承受低性能片内基准电压源带来的痛苦时,往往不得不选择 DAC 和外部基准电压源。他们不能指望片内基准电压源的性能,因为这些电压源在各种温度下变化极大,而且往往缺少最大 TC 规格,无法用作系统基准电压源。

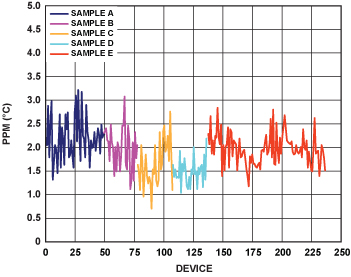

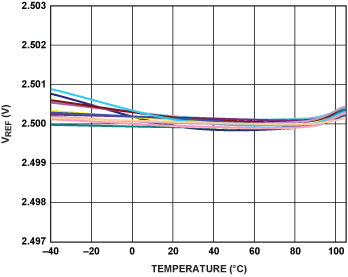

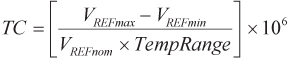

AD5686R 打破了这一惯例。这款四通道、电压输出、16 位 nanoDAC+® 数模转换器提供了 2.5 V 片内基准电压源,并且最大温度漂移为 5 ppm/°C(通常为 2 ppm/°C)。这一性能水平与独立基准电压源的性能水平相当,使得片内基准电压源可以取代系统基准电压源,从而节省空间、成本和功耗。5-ppm/°C 的最大漂移规格允许进行精密误差量计算。图 1 和图 2 显示了 AD5686R’ 片内基准电压源的性能。图 1 显示了五个单独采样批次的数百个 DAC 的温度系数散布图。图 2 显示了九个 DAC 在 –40°C 至 +105°C 温度范围内的实际输出电压。

方法:对于参考电压,温度系数 (TC) 通常使用箱式方法确定,该方法在规定的温度范围内评估最大电压变化。TC 以 ppm/°C 为单位,按照以下方程式计算

其中

VREFmax 是在温度范围内测得的最大基准电压输出。

VREFmin 是在温度范围内测得的最小基准电压输出。

VREFnom 是标称基准输出电压。

TempRange 是规定的温度范围 (°C)。

低温系数是通过加热生产中零件并微调输出电压以补偿随温度变化的曲线而得出的。紧密配合可以确保电阻差异不会影响基准电压源的性能,并且还让 DAC 达到极其出色的 ±2-LSB 积分非线性 (INL) 规格。

关于 AD5686R/AD5685R/AD5684R

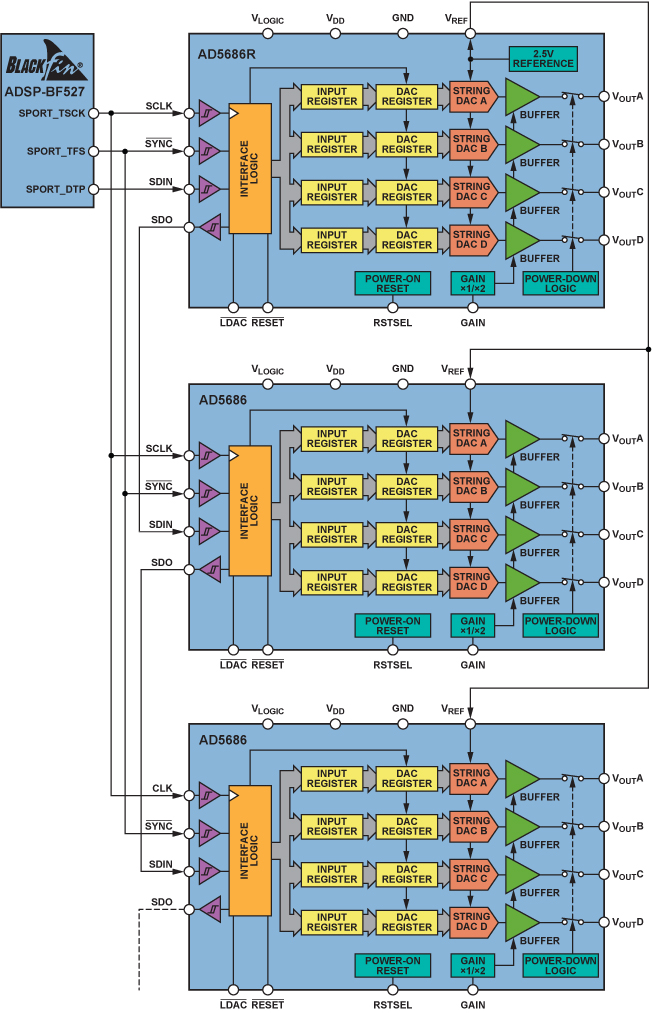

AD5686R/AD5685R/AD5684R 属于 nanoDAC+ 系列,它们是四通道、低功耗、16/14/12 位 DAC,提供经过缓冲的电压输出。市场对精度高、操作简便且封装尺寸小巧的数模转换器的需求日益增多,nanoDAC+ 系列正是为了满足这一需求而开发的。这些新器件包含已默认启用的片内 2.5V 2-ppm/°C 基准电压源。增益选择引脚可将满度输出设置为 2.5 V (GAIN = 1) 或 5 V (GAIN = 2)。这些器件采用单个 2.7 V 至 5.5 V 电源,具有 0.1% 的最大增益误差、2 mV 的最大偏置误差和保证的单调性。它们提供 LFCSP (3-mm × 3-mm) 和 TSSOP 封装,并且 4-kV ESD 额定值突显了它们具有极其强大的性能。DAC 输入可通过 1.8 V SPI 兼容接口进行编程。上电复位电路会确保 DAC 输出电源最多为 0 V,并且保持此状态,直到进行有效的写入。复位引脚允许进行异步复位。基准电压源输出引脚允许在外部将片内基准电压源用作系统基准电压源。菊花链功能可以实现具有更多通道数量的系统。外部基准电压源型 AD5686/AD5685/AD5684 允许以最低的成本在所有通道上共用单个基准电压源。图 3 显示了多通道系统中使用这些 DAC 的部分。

电压切换式 16 位 DAC 提供低噪声、快速设置和更佳线性度

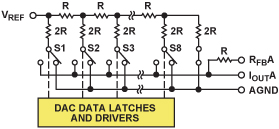

电阻梯式乘法 DAC 基于改变游戏规则的 10 位 CMOS AD7520—大约 40 年前推出—最初与反相运算放大器配合使用,并且提供了便于虚拟接地的放大器求和点 (IOUTA)(图 4)。

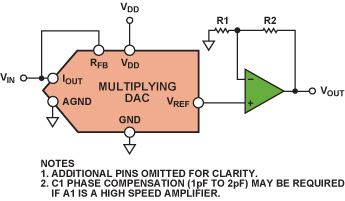

然而,它们还可以在少数情况下用于那些提供同相电压输出的电压切换式配置中,并将运算放大器用作电压缓冲器(图 5)。在这里,基准电压 VIN 应用于 IOUT,并且输出电压 VOUT 可在 VREF 处提供。不久会推出针对此目的优化的 12 位版本。

快速发展到现在:随着单电源系统越来越普遍,设计师面临的挑战是如何在更高电压下尽力保持出色的性能水平,同时保持对功耗的控制。能够在此模式下使用的、具有更高分辨率(多达16 位)的器件受到了市场的更多青睐。

在电压切换模式下使用乘法 DAC 的明显好处是不会发生任何信号反相,因此正基准电压会产生正输出电压。但在这种模式下使用时,R-2R 梯形架构也存在缺点。与在电流控制模式下使用相同的 DAC 相比,与 R-2R 梯形网络串联使用的 N 通道开关的非线性电阻会降低积分非线性 (INL)。

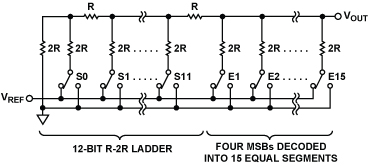

AD5541A 等新型高分辨率 DAC(如图 6 所示)已经开发出来,旨在克服乘法 DAC 的局限性,同时保持电压切换的优势。通过使用部分分段的 R-2R 梯形网络和辅助开关,AD5541A 在 16 位分辨率下提供 ±1-LSB 的精度,而且无需调整整个指定温度范围(−40°C 至 +125°C)、11.8 nV/&radIC;Hz 噪声和 1-µs 建立时间。

性能特性

建立时间:图 7 和图 8 比较了处于电压模式下的乘法 DAC 和 AD5541A 的各自建立时间。当输出上的容性负载减至最低时,AD5541A 的建立时间约为 1 µs。

噪声谱密度:表 1 比较了 AD5541A 和乘法 DAC 的噪声谱密度。AD5541A 在 10 kHz 时的性能略微好于乘法 DAC,但在 1 kHz 时的性能远远胜出乘法 DAC。

表 1. AD5541A 和乘法 DAC 的噪声谱密度对比| DAC | NSD @ 10 kHz (nV/√Hz) | NSD @ 1 kHz (nV/√Hz) |

| AD5541A | 12 | 12 |

| MDAC | 30 | 140 |

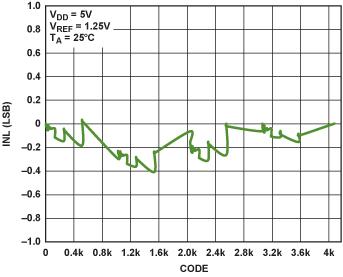

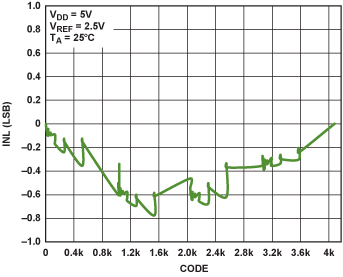

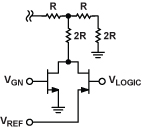

积分非线性:积分非线性 (INL) 用于测量 DAC 的理想输出与在去除增益和偏置误差之后的实际输出之间的最大偏差。与 R-2R 网络串联使用的开关会影响 INL。乘法 DAC 一般采用 NMOS 开关。在电压切换模式下使用时,NMOS 开关的来源连接到基准电压,漏极连接到梯形网络,并且栅极由内部逻辑驱动(图 9)。

为了使电流流入 NMOS 器件,VGS 必须大于阈值电压 VT。在电压切换模式下,VGS = VLOGIC – VIN 必须大于 VT = 0.7 V。

乘法 DAC 的 R-2R 梯形网络经过专门设计,可以通过每个支腿均匀分配电流。这要求整体接地电阻(从每个支腿的顶部查看)必须完全相同。这可通过调整开关的小大来完成(每个开关的大小与其导通电阻成正比)。如果一个支腿中的电阻发生了变化,流过此支腿的电流将会改变,进而导致线性误差。VIN 不能太大,否则会关闭开关,但它必须大到足以将开关电阻保持在较低的水平,因为 VIN 的变化会影响 VGS,进而导致导通电阻发生非线性变化,如下所示:

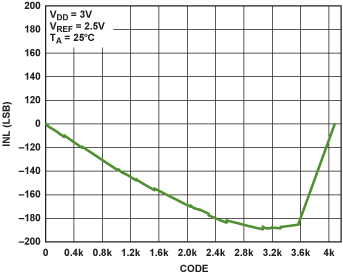

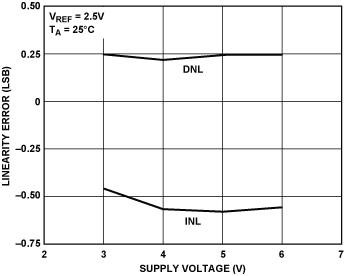

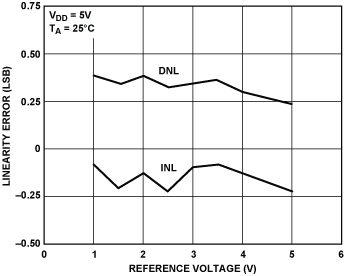

这种导通电阻的变化会使电流失衡并降低线性度。因此,乘法 DAC 的电源电压不能减少太多。反过来,为了保持线性度,基准电压不应比 AGND 高出 1 V 以上。通过使用 5 V 电源,当从 1.25 V 基准电压源移至 2.5 V 基准电压源时,线性度开始降低,如图 10 和 11 所示。 当电源电压降低到 3 V 时,线性度完全消失,如图 12 所示。

为尽可能减少此影响,AD5541A 采用了互补 NMOS/PMOS 开关,如图 13 所示。现在,开关的总导通电阻来自 NMOS 和 PMOS 开关的并联电阻。如前所述,NMOS 开关的栅极电压由内部逻辑控制。内部产生的电压 VGN 会设置理想的栅极电压,以平衡 NMOS 的导通电阻与 PMOS 的导通电阻。开关的大小会调整以与代码成比例,因此导通电阻将会与代码成比例。这样,电流将会调整,并且精度将得以保持。当基准输入检测到随代码变化的阻抗时,它将由低阻抗源驱动。

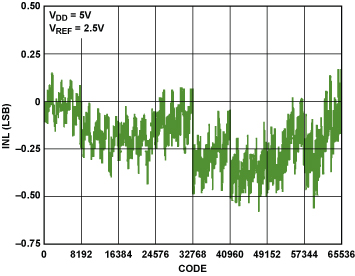

图 14 和 15 显示了采用 5 V 和 2.5 V 基准电压源的 AD5541A 的 INL 性能。

图 16 和图 17 显示线性度在宽泛的基准和电源电压范围内变化很小。DNL 的性能表现与 INL 类似。AD5541A 线性度在温度和电源电压上指定;基准电压可以在 2.5 V 和电源电压之间变化。

关于 AD5541A 的更多信息

AD5541A 串行输入、单电源、电压输出 nanoDAC+ 数模转换器可以提供 16 位分辨率,并且具有 ±0.5-LSB 的典型积分和差分非线性。它非常适用于那些在电压切换模式下使用乘法 DAC 的应用场合。它在温度和电源电压上都表现良好,取得优异的线性度,并且可用于需要精密直流性能和快速建立时间的 3 V 至 5 V 系统。通过使用范围介于 2 V 和电源电压之间的外部基准电压,未经缓冲的电压输出可在 0 V 到 VREF 的范围内驱动 60 kΩ 的负载。该器件提供 1-µs 的建立时间(½ LSB)、11.8 nV/√Hz 的噪声以及低故障率,非常适合部署在众多不同的医疗、航空航天、通信和工业应用领域中。它的 3 线、低功率 SPI 兼容串行接口可以处理高达 50 MHz 的时钟输入信号。AD5541A 采用单个 2.7 V 至 5.5 V 电源,吸入电流仅为 125 µA。它提供 8 引脚和 10 引脚 LFCSP 以及 10 引脚 MSOP 封装,工作温度范围为 –40°C 至 +125°C,起价为 6.25 美元(1000 件)。

高速电流输出 DAC 缓冲器

由于不会增加噪声或消耗功率,变压器通常被认为是将高速电流输出 DAC 的互补输出转换成单端电压输出的最佳选择。虽然变压器对高频信号操作良好,但是它们不能处理许多仪表和医疗应用所需的低频信号。这些应用场合需要使用低功率、低噪声和高速放大器以将互补电流转换成单端电压。下面介绍的三个电路均可接受来自 DAC 的互补输出电流并提供单端输出电压。后两个电路的失真与变压器解决方案进行了对比。

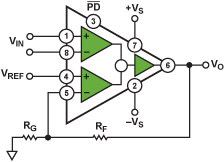

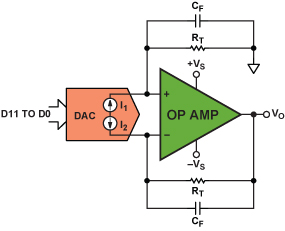

差分放大器:AD8129 和 AD8130 差分-单端放大器(图 1)用于第一个电路(图 2)。对于高频信号,它们具有极高的共模抑制能力。AD8129 对 10 以上的增益是稳定的,AD8130 则是单位增益稳定。其用户可调的增益可以通过两个电阻 RF 和 RG 的比率进行设置。无论增益如何设置,AD8129 和 AD8130 的引脚 1 与引脚 8 上均具有非常高的输入阻抗。基准电压(VREF,引脚 4)可以用于设置偏置电压,然后将它乘以与差分输入电压相同的增益。

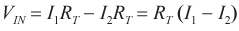

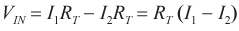

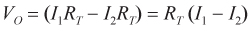

方程式 1 和 2 显示了放大器的输出电压与 DAC 的互补输出电流之间的关系。终端电阻 RT 执行电流至电压的转换;RF 和 RG 的比率决定增益的大小。在方程式 2 中,VREF 设置为 0。

| (1) |

| (2) |

在图 2 中,此电路采用了四通道、高速、低功耗 14 位 DAC,在此,互补电流输出级增加了低功耗 DAC 的速度并减小了低功耗 DAC 的失真。

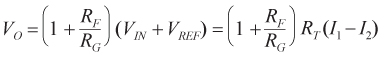

图 3 显示了在两个电源电压值下使用 DAC 和 AD8129 时的无杂散动态范围 (SFDR),该范围作为频率的函数,并且 RF = 2 kΩ,RG = 221 Ω,RT = 100 Ω,VO = 8 V p-p。之所以在这里选择 AD8129,是因为它可以提供较大的输出信号、对 G = 10 稳定并且比 AD8130 具有更高的增益带宽积。在两种情况下,SFDR 通常均优于 55 dB,超过 10 MHz,并且在较低电源电压下改善了大约 >3 dB 。

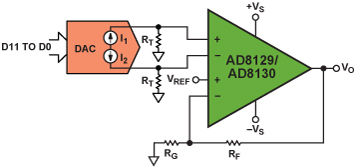

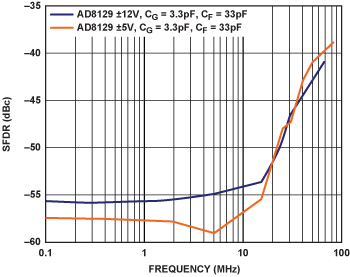

单位增益运算放大器:第二个电路(图 4)使用包含两个 RT 电阻的高速放大器。放大器可以简单地通过 RT 将互补电流 I1 和 I2 转换成单端输出电压 VO。这一简单的电路不允许将放大器用作增益模块进行信号放大。

方程式 3 显示了 VO 和 DAC 输出电流之间的关系。失真数据通过与 RT 并联的 5 pF 电容器进行测量。

| (3) |

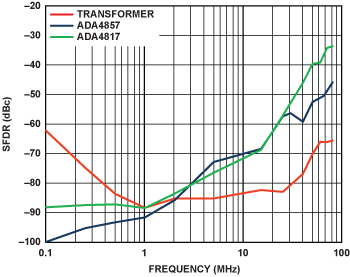

为了展示此电路的性能,DAC 与 ADA4857 和 ADA4817 运算放大器搭配使用,并且 RT = 125 Ω(CT = CF = 5 pF,与 RT 并联,以实现稳定性和低通滤波)。单 ADA4857-1 和双 ADA4857-2 是单位增益稳定、高速、电压反馈型放大器,具有低失真、低噪声和高压摆率。作为超声、ATE、有源滤波、ADC 驱动器等各种应用的理想解决方案,它具有 850 MHz 带宽、2800 V/μs 压摆率和 10 ns 建立时间(0.1%)—所有均采用 5 mA 的静态电流工作。凭借宽泛的电压范围(5 V 至 10 V),ADA4857-1 和 ADA4857-2 成为那些要求宽动态范围、出色精度、高速和低功耗的系统的理想选择。

单 ADA4817-1 和双 ADA4817-2 FastFET ™ 放大器是单位增益稳定、超高速度、电压反馈型运算放大器,具有 FET 输入。它们基于 ADI 专有的超快速互补双极型工艺 (XFCB) 开发,具有超低的噪声(4 nV/√Hz 和 2.5 fA/√Hz)和非常高的输入阻抗。凭借 1.3 pF 的输入电容、2 mV 的最大偏置电压、低功耗 (19 mA) 和宽泛的 −3 dB 带宽 (1050 MHz),它们成为数据采集前端、光电二极管前置放大器和其他宽带跨阻抗应用场合的理想之选。它们具有 5 V 至 10 V 的电源电压范围和单或双电源工作能力,适合在有源滤波、ADC 驱动、DAC 缓冲等众多应用场合中工作。

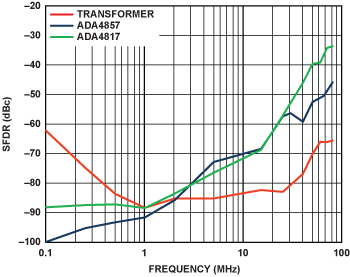

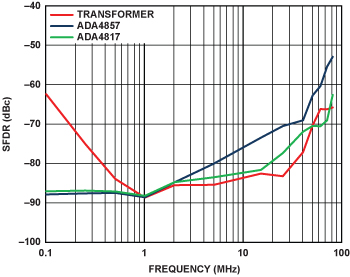

图 5 比较了这一电路与使用变压器的电路的失真和频率( VO = 500 mV p-p)。变压器的失真小于放大器,后者在高频下具有更低的增益,但其失真在低频下变得越来越差。从图中看出,可在有限的范围内实现近 90 dB 的 SFDR,并且在 10 MHz 之前优于 70 dB。

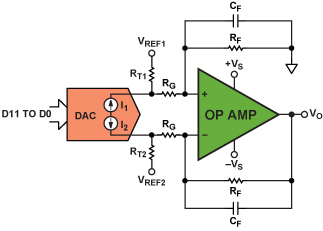

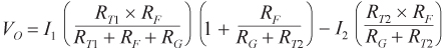

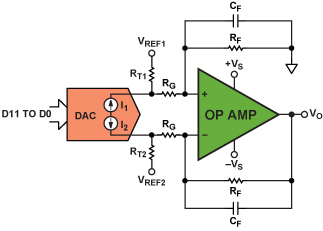

具有增益能力的运算放大器:第三个电路(图 6)也使用了相同的高速运算放大器,但它包含一个将放大器与 DAC 隔离的电阻网络,这允许设置增益,并可以灵活使用两个基准电压(VREF1 和 VREF2)之一来调节输出偏置电压。

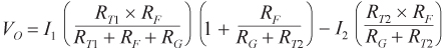

方程式 4 定义了在 VREF1 = VREF1 = 0 时 DAC 输出电流和放大器输出电压之间的关系。为了匹配用于监视 DAC 的放大器网络的输入阻抗,两个终端电阻 RT1 和 RT2 必须单独设置,同时考虑放大器的特性。

| (4) |

图 7 比较了此配置中放大器的失真以及变压器电路的失真。RT1 = 143 Ω,RT2 = 200 Ω,RF = RG = 499 Ω,CF = 5 pF—(实现稳定性和高频滤波),—以及 RL = 1 kΩ。从图中看出,在高频时,ADA4817 的性能与变压器相当,并且在 70 MHz 之前始终优于 −70 dBc SFDR。在低频时,与变压器相比,两个运算放大器保持了卓越的保真度。

本文通过比较电路在使用放大器和变压器时的性能,展示了在将低失真、低噪声、高速放大器用作 DAC 缓冲器时的一些优点。它还比较了三个使用两种不同放大器架构的应用电路,并且提供了在使用 DAC 和 AD8129、ADA4857-1/ADA4857-2 以及 ADA4817-1/ADA4817-2 放大器时的测量数据示例。数据表明,在频率小于 1 MHz 时,放大器的性能优于变压器,并且在 80 MHz 之前,放大器的性能接近变压器的性能。在功耗和失真之间做出取舍时,放大器的选择是非常重要的。

客服微信

客服微信 查ic网订阅号

查ic网订阅号