随着医疗、消费电子和工业市场上的便携式手持仪器仪表日趋向尺寸更小、重量更轻、电池(或每次充电)续航时间更长、成本更低且通常功能更多方向发展,低功耗已经成为如今电池供电模数转换器应用的一项关键要求。即使是在非电池供电的应用中,低功耗的好处也不容忽视,因为低功耗系统无需散热器或风扇也能工作,因而尺寸更小、成本更低,而且更加可靠,同时也"更加绿色环保"。此外,许多设计人员在设计产品时都面临一个挑战,即在增强产品功能或性能的同时降低或者至少不得超过当前的功耗预算。

当今市场上品种繁多的ADC则使得选择符合特定系统要求的最佳器件变得更加困难。如果说低功耗是必须的条件,那么除了评估速度和精度等常见的转换器性能特性之外,还需要考虑更多性能指标。了解这些指标以及设计决策会对功耗预算有何影响,对于确定系统功耗和电池寿命计算非常重要。

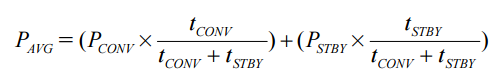

ADC的平均功耗是转换期间所用功耗、不转换时所用功耗以及各模式下所用时间的函数,如等式1所示。

| (1) |

PAVG = 平均功耗。

PCONV = 转换期间的功耗。

PSTBY = 待机或关断模式下的功耗。

tCONV = 转换所用时间。

tSTBY = 处于待机或关断模式的时间。

转换期间所用功耗通常远大于待机功耗,因此如果处于待机模式的时间增加,平均功耗会显著降低。逐次逼近(SAR)型转换器尤其适合此类工作模式

影响系统电源使用情况的最大因素之一是板上电源的选择。对于便携式应用,系统通常由3 V纽扣式锂电池直接供电。这样就无需使用低压差稳压器,从而节省电能、空间和成本。非电池应用也可受益于具有低VDD电源电压范围的转换器,因为功耗与输入电压成正比。为VDDADC选择最低可接受VDDVDD将可降低功耗。

针对低功耗应用的所有ADC都具有关断或待机模式,以便在闲置期间节省电能。ADC可以在单次转换之间关断,或者以高吞吐速率突发执行一阵转换,在这些突发之间关断ADC。对于单通道转换器,工作模式的控制功能可以集成到通信接口,或者在完成一次转换后自动进行。

将模式控制集成到通信接口的好处是可以减少引脚数量。这样可以降低功耗,因为要驱动的输入更少,同时漏电流也更小。此外,引脚数量越少,封装尺寸也就越小,同时MCU所需的I/O也越少。无论采用何种控制方法,只要谨慎使用这些模式都能显著节省电能。

顾名思义,关断模式会关闭部分ADC电路,从而降低功耗。关断后电路重新启动转换所需的时间决定可有效使用此类模式的吞吐速率。对于带有内部基准电压源的ADC,重新启动时间将由基准电容重新充电所需的时间决定。采用外部基准电压源的模数转换器需要足够的时间在重新启动时正确跟踪模拟输入。

对于当今市场上的所有ADC,功耗均与吞吐速率成正比。功耗由静态功耗和动态功耗组成。静态功耗是恒定的,动态功耗则和吞吐速率呈线性变化关系。因此,在满足应用要求的前提下尽可能选择最低的吞吐速率可以省电。

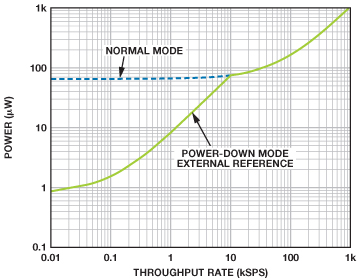

图1所示为AD7091R, 的典型功耗与吞吐速率的函数关系,该器件是ADI公司最近推出的超低功耗ADC。图中还比较了利用器件的关断模式(尤其是在较低吞吐速率条件下)可以带来怎样的额外省电效果。AD7091R的吞吐速率和关断模式利用率取决于器件的重新启动时间,以及基准电容的重新充电时间,因为AD7091R具有片内基准电压源。基准电容重新充电所需的时间取决于电容大小,以及片内基准电压源重新启动时电容的剩余电荷水平。

ADC中启动转换请求的最常见方法是采用专用转换输入引脚或通过串行接口进行控制。采用专用输入引脚(CONVST)时,转换在下降沿启动。然后,由片内振荡器控制转换,转换完成后,可通过串行接口回读结果。因此,转换始终以恒定的最佳速度运行,允许器件在转换完成时进入低功耗模式,从而节省电能。

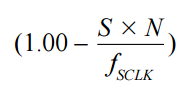

当ADC中的采样时刻由片选(CS)上的下降沿启动时,转换由内部采样时钟(SCLK)信号控制。SCLK频率将会影响转换时间和可实现的吞吐速率,进而影响功耗。SCLK速率越快,转换时间就越短。转换时间越短,器件处于低功耗模式的时间比例相对于正常模式就越大,因此可以实现显著的省电效果。也就是说,如果每次转换需要N SCLK周期,那么对于每秒执行S次转换,SCLK开关的总时间为S S × N/fSCLK每秒内的静态时间如等式2所示。

| (2) |

因此,对于给定的每秒采样次数,随着fSCLK增加,每秒内的静态时间也会增加。

例如,假设完成转换并读取结果需要16个SCLK周期,则对于采样速率为100 kSPS且SCLK为30 MHz的系统,静态时间所占比例为94.67%,也就是说转换所用时间占5.33%(每秒内53.3 ms)。当SCLK为10 MHz时,同一系统的静态时间仅占84%,也就是说转换用时为160 ms。因此,要实现最佳功耗性能,转换器应以可支持的最高SCLK频率工作。

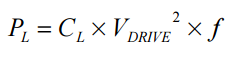

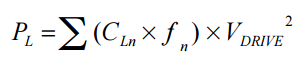

针对低功耗应用而设计时,有个很重要的参数却往往被忽视,即输出引脚(尤其是SCLK、CS和SDO等通信接口引脚)上的容性负载,因为这些I/O变量会在转换过程中不断改变状态。输出端上的容性负载等于驱动器IC本身的引脚电容、输入引脚的引脚电容以及PCB走线电容之和。走线电容通常都很小,处于飞法范围内,因此意义不大。为容性负载充电所需的功率(PL)是负载(CL)、驱动电压(VDRIVE)以及充电频率(f)的函数,其定义如等式3所示。

| (3) |

因此,整个系统的功率等于负载电容(CLn)和开关频率(fn)乘积之和乘以驱动电压的平方。

| (4) |

由于ADC驱动SDO引脚,主机微控制器驱动CS、CONVST和SCLK引脚,因此可通过尽可能减少所有器件的引脚电容来实现最低功耗。

对于CS和CONVST引脚,开关频率仅取决于吞吐速率。如前所述,SCLK频率应设置为可支持的最大频率,以便降低功耗。这并不矛盾:重要的是SCLK并不是自由运行——它应该仅在尽可能短的时间内激活,以便在SDO线路上传播每个位检验的结果并控制转换过程。这点依器件和分辨率而定,但通常为每位一个周期,再加上一些开销;对于12位转换器SPI接口,每次采样约为16个SCLK周期。因此,SCLK的最小频率为所需周期数乘以吞吐速率。

SDO线路的频率取决于吞吐速率和转换结果。虽然这个无法进行控制,但是设计人员应该了解它会对转换功耗造成什么影响。当结果为101010…序列时,功耗最大;当结果为全1或全0时,功耗最小。

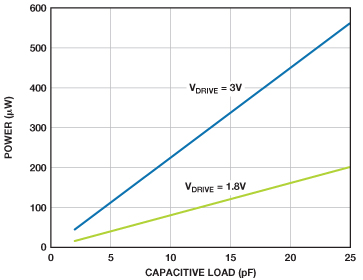

除了降低吞吐速率之外,减小VDRIVE电压也可明显降低功耗。模数转换器通过单电源引脚或单独的电源来为模拟电路和数字接口供电。使用单独的VDRIVE电源时,设计灵活性更高并且无需电平转换器,因为模数接口电压可与SPI主机的电压相匹配。为VDRIVE 选择可用的最低电压时,系统功耗将最低。

图2比较了12位ADC在VDRIVE值为3 V和1.8 V时标准SPI接口(含CS、SDO和SCLK)的典型功耗要求与总容性负载的关系,其中吞吐速率为100 kSPS、每次转换16个SCLK周期以及最差情况SDO输出为1010。

ADC电路设计的其它典型构成要素包括基准电压源和运算放大器。不言而喻,应针对低功耗认真选择这些元件。有些基准电压源带有关断模式,以便在非活动期间降低功耗。放大器选择视应用而定,因此应考虑到系统吞吐速率,以确保所选放大器能够使ADC性能达到最佳,同时使功耗降至最低。

12位AD7091R专为低功耗应用而设计,具有一个SPI接口和一个片内精密2.5 V基准电压源,采样速率为1 MSPS。转换通过CONVST引脚启动。片内振荡器控制转换过程,使之能够优化功耗。引脚电容很小,最大值为5 pF。宽输入电压范围(2.7 V至5.25 V)允许集成到更广泛的应用中,而不仅仅是电池供电应用。单独的1.65 V至5.25 V VDRIVE电源则可降低功耗,并提高系统集成能力。

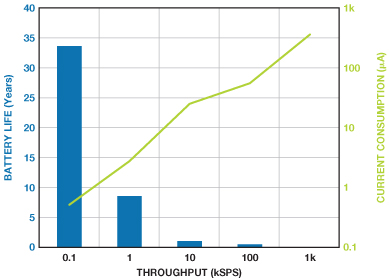

采样速率为1 MSPS且VDD为3 V时,AD7091R功耗为349 μA(典型值)。由于其功率与吞吐速率成正比,因此100 kSPS时静态电流为55 μA。不执行转换但基准电压源激活时,静态电流为21.6 μA;在关断模式下,电流仅为264 nA。AD7091R采用10引脚MSOP或LFCSP封装。

驱动AD7091R的典型放大器包括 AD8031(针对快速吞吐速率应用)和 AD8420 f(针对较低带宽应用)。采用2.7 V电源供电时,AD8031的静态功耗为750 μA(典型值);采用5 V电源供电时,AD8420的静态功耗为70 μA(典型值)。

图3所示为通过CR2032锂电池供电时AD7091R的典型功耗和计算得出的电池寿命。可以清楚看出,随着吞吐速率降低,电池寿命明显延长。

与多数其它ADC相比,AD7091R可以在功耗预算上实现显著节省效果。例如,与最接近的可用竞争产品(一款不带内部基准电压源的器件)相比时,对于1 MSPS吞吐速率,AD7091R可使功耗降低3倍(对于3 V电源,其功耗典型值为1 mW,而比较产品的功耗典型值为3.9 mW)。这相当于将CR2032电池寿命延长400小时。考虑需要外部基准电压源的其它器件时,节省效果更为明显。

结论

除延长电池寿命之外,降低功耗还有其它很多好处。产生的热量变少,进而使尺寸变小。稳定性因温度应力降低而得以提高。由于采用更小的元件,因此PCB尺寸得以缩小;另外,由于无需散热器之类的配件,因此元件数量得以减少;这些使系统成本降低。

本文概述了系统设计人员在采用ADC的设计中优化功耗时应考虑到的几个重要因素和好处。

我邀请您在中文技术论坛 上的 ADI社区 on 低功耗SAR型模数转换器发表评论。

参考电路

Casamayor, Mercedes and Claire Croke. “How to Save Power in Battery Applications Using the Power-Down Mode in an ADC.” Analog Dialogue, Vol. 37, No. 3, pp. 3-9, 2003.

客服微信

客服微信 查ic网订阅号

查ic网订阅号