随着网络技术发展,移动网络速度不断提升,为移动互联网业务带来了良好的发展条件,但同时带来的爆炸式数据流量增长对运营商形成了巨大的压力,传统的扩容方式就是不断增加X86服务器,以应对巨大的用户访问需求,但是增加服务器随之带来的能源损耗让运营商不堪重负,电费成为最大的运营成本。因此,数据中心运维人员不得不寻求更高性能的服务器。

移动互联网的春天,FPGA新的市场机遇

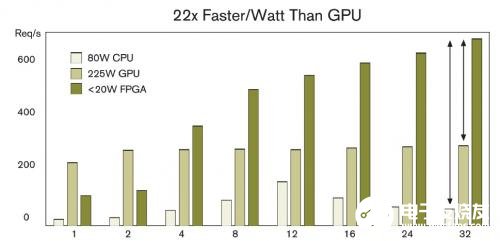

随着半导体技术的发展,数据中心运维人员采用通过易于编程的多核CPU和GPU来开发应用,但CPU和GPU都遇到了单位功耗性能的瓶颈--当增加高分辨率视频、图像识别、深度包检测以及并行算法处理等特殊要求时,就很难让带有标准CPU或GPU的PCI Express开发板将功耗预算保持在25瓦以内。研究发现,基于FPGA的应用加速想比CPU/GPU实现方案,单位功耗性能可提升25倍,而时延则缩短了50到75倍,与此同时还能实现出色的I/O集成(PCIe、DDR4SDRAM接口、高速以太网等)。换言之,FPGA 能在单芯片上提供高能效硬件应用加速所需的核心功能,并同时提供每个开发板目标功耗低于25W的解决方案。

FPGA的优势固然明显,但是负责数据中心运维人员基本全部为软件工程师,他们对FPGA的硬件知识高度缺乏,如果他们想通过FPGA实现自己想要的功能,首先需要编写程序,然后让硬件工程师转化为硬件开发语言才能够实现,这在无形中增加了开发成本,同时加长了开发周期,让软件工程师直接控制FPGA成为很多运营商的当务之急。

软件工程师也能玩转FPGA

软件工程师是否要一直受制于硬件知识匮乏的不足?答案是否定的。赛灵思在2014国际超算大会上推出了针对OpenCL、C和C++的SDAccel开发环境,这款软件带有用于代码开发、特性分析与调试的Eclipse集成设计环境(IDE),可提供类似于CPU/GPU 的工作环境,开发人员可以快速上手应用。赛灵思公司亚太区销售与市场副总裁杨飞介绍,SDAccel具有三大优势:第一,首款针对OpenCL、C和C++的架构优化编译器;第二,在FPGA上首次实现完全类似CPU/GPU的开发体验;第三,在FPGA上首次实现完全与CPU/GPU的运行时间体验。

SDAceel提供OpenCL、C、C++编译能

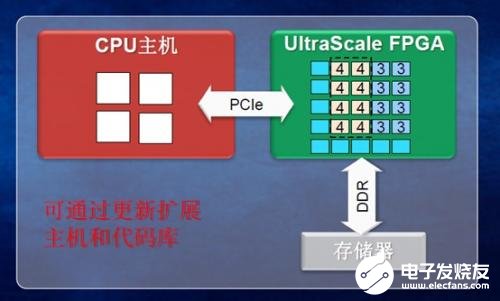

杨飞强调,借助SDAccel,开发人员能够使用其熟悉的工作流程优化应用,而且即便之前没有FPGA使用经验,也能受益于FPGA平台的优势。集成设计环境(IDE)不仅可提供编码模板和软件库,而且还能对各种开发目标进行编译、调试和特性分析,如在X86平台上仿真、使用快速仿真进行性能验证以及在FPGA处理器上进行本地执行等。IDE可在数据中心用FPGA平台上执行应用。该平台配套提供面向所有支持开发目标的自动仪器插入功能。此外,SDAccel还经过精心设计,使CPU/GPU开发人员能够轻松将其应用迁移到FPGA上,同时还可在他们熟悉的工作流程中维护和复用OpenCL、C和C++代码。SDAccel环境包括编程器用IDE、基于C语言的FPGA优化库,以及数据中心用现成商用(COTS)平台。

SDAccel开发平台

SDAccel库包括用于高性能低功耗实现方案的内置OpenCL函数、DSP、视频以及线性代数库。针对特定领域加速,赛灵思联盟合作成员Auviz Systems提供了精心优化的OpenCV和BLAS OpenCL兼容型软件库。FPGA加速卡的第三方合作商有Alpha Data、Convey、PICo Computing,预计2015年年初还将增加新成员。第三方合作商不属于赛灵思公司,他们在赛灵思FPGA硬件基础上开发应用方案。

FPGA可实现动态重加载

据统计,软件从业者是硬件从业者的几十倍,赛灵思开发SDAccel的目的不仅扩大了市场范围,更重要的是为软件工程师提供了便捷服务。移动互联网飞速发展,大数据纷飞,云计算如雷贯耳,高通日前宣布进入服务器领域(高通服务器芯片,会重演英特尔的历史命运吗?),直接对抗X86架构,孰胜孰负有待分晓,不管谁会称霸服务器市场,FPGA的重要角色都不可或缺,“FPGA不是要代替服务器,而是辅助服务器提高运行速度,降低功耗。”杨飞补充,“赛灵思的业务模式是软件几乎免费,只象征性收费,这对于用户来说可以节省更多成本。”

客服微信

客服微信 查ic网订阅号

查ic网订阅号