1 引言

工业CT 机运动控制系统往往需要对多个轴的运动进行精确、实时控制,在以往的系统中多采用工控机+多块板卡的结构进行运动控制器的设计。随着工业CT 机整体功能日趋复杂,整体系统对运动控制系统的体积、成本、功耗等方面的要求越来越苛刻。另一方面,运动控制系统控制的轴数越来越多、控制精度要求越来越高、控制对象的实时性要求越来越强。

现有的工控机+多块板卡组成的控制系统逐渐呈现出运动控制方面的劣势。ARM+FPGA的硬件方案,将工控机从现有的运动控制系统中解放出来,取而代之的是体积小、功耗低、功能强的ARM 处理器。强大的嵌入式Linux 操作系统保证ARM 处理器的功能可以发挥到最佳。

2 硬件系统关键技术设计与实现

本系统采用ARM+FPGA的结构进行运动控制系统的设计,与目前应用中常见的IPC(IndustrialPersonal Computer)+板卡的运动控制系统相比具有以下优点:

(1) 采用FPGA 完成运动控制细节任务,实现硬件软化的设计思想。即具有软件可编程、可重构的特性,又有硬件高性能、高可靠、高一致性的优点。

(2) 采用嵌入式应用方案与现有IPC+板卡结构相比无论从体积、成本、还是性能方面相比都具有较大的优越性。

(3) FPGA 具有高速并行的执行能力,系统的实时性能得到较大的提高。

(4) 将ARM 中操作底层硬件的驱动程序进行打包,方便应用程序调用,可以较快完成用户的二次开发。

2.1 硬件系统总体设计

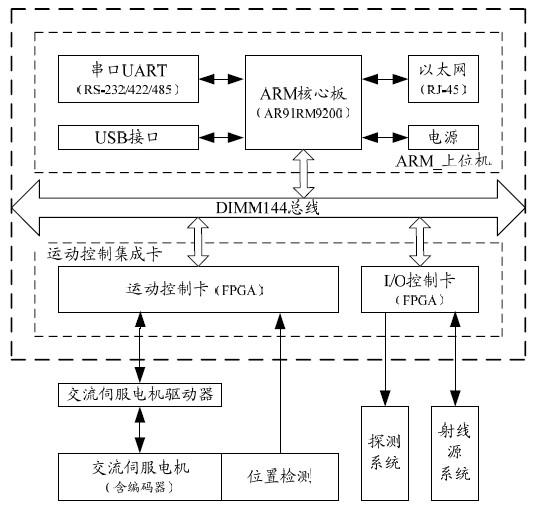

工业CT 运动控制系统结构如图1 所示。该系统以Atmel 公司一款ARM9 核处理器AT91RM9200和Altera 公司的Cyclone 系列芯片EP1C6Q240C8 为核心。ARM9 作为主控芯片负责整个系统的控制,通过AHB[3]总线协调与FPGA 之间的数据交换,并将接收到的数据通过网络发送到工业控制计算机进行图像的处理与重建。FPGA 则负责接收数据采集系统的串行数据,并把其转化成并行数据存入FPGA 的RAM 中,同时对ARM 发出中断请求响应,通知ARM9 读取。AT91RM9200、SDRAM、FLASH 以及电源等基本外围电路构成嵌入式Linux 运行的最小系统,而FPGA 最小系统则由EPlC6Q240C8、时钟电路、配置接口等组成。然后两者通过高速AHB 总线进行连接,实现数据的快速传输。

图1 工业CT 运动控制系统结构图

2.2 ARM 与FPGA 接口设计

在系统中ARM 作为通用处理器,用来实现系统任务的触发、系统命令的发送和任务的调度等功能。

FPGA 作为ARM 的外设,用来对ARM 经地址数据总线传送过来的命令进行解析,并最终按照ARM 命令的要求,完成脉冲发送和脉冲计数的功能及具体的运动控制细节任务。

两块FPGA通过各自的地址/数据总线与ARM的地址/数据总线连接起来,双方可以进行双向的数据交换。

ARM 与FPGA 通过地址选通信号线连接起来,两块FPGA 各自作为ARM 的外设芯片,运行在独立的地址空间,地址选通信号结合地址总线实现ARM对 FPGA 内部寄存器的寻址。

3 软件系统关键技术设计与实现

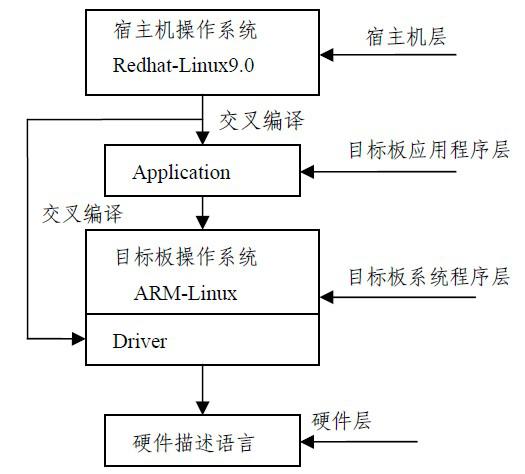

系统软件总体采用分层思想进行设计。整个系统软件主要由宿主机操作系统、宿主机开发软件、目标板操作系统、目标板底层硬件驱动程序、目标板应用程序、HDL 硬件描述语言组成。宿主机操作系统选择REDHAT-LINUX9.0 版本;宿主机开发软件主要由一些交叉编译环境、汇编和链接工具组成;目标板操作系统选用ARM-LINUX 操作系统;目标板应用程序使用C 代码进行编写;HDL 语言用于对FPGA 的功能进行描述。

软件系统分层示意图如图2 所示。在宿主机中,交叉编译将要在目标板平台上运行的应用程序代码和底层硬件驱动程序代码展开,然后通过宿主机与目标板之间的硬件接口传递到目标板中,目标板通过底层硬件驱动程序控制FPGA 模块中配置的各功能寄存器,从而完成具体的控制任务。本文重点介绍FPGA内部功能模块的设计及驱动程序接口设计。

图2 软件系统分层示意图

3.1 FPGA 内部关键功能模块设计

FPGA 不擅长对数据进行运算处理,但本系统对每个轴的控制都要进行相应的运算,因此在每个轴的控制模块设计中尽量不涉及复杂的算法实现,算法部分留给ARM 进行处理。原则上FPGA 仅仅接收经ARM 进行处理过的数据,而后按照ARM 主控单元的处理结果进行处理。

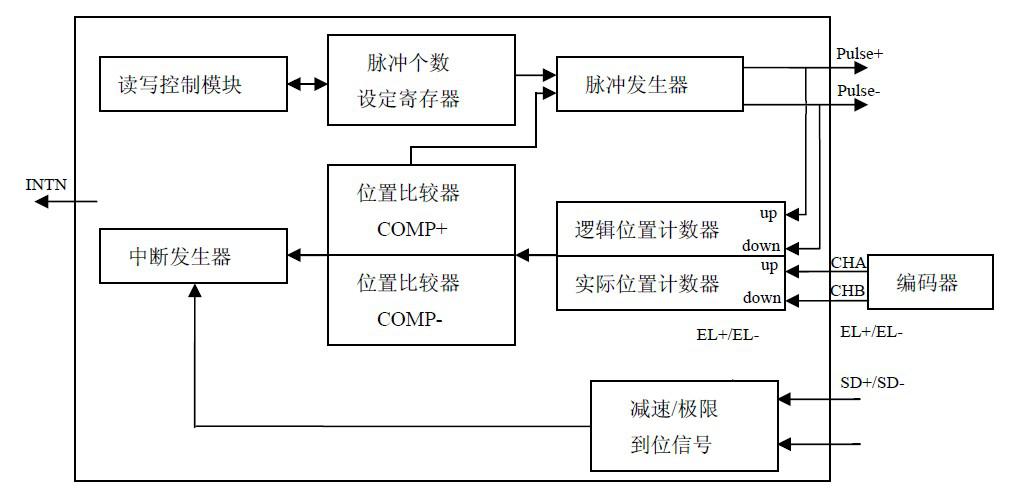

单轴控制模块框图如图3 所示。在每个位置管理单元中都配置了两个计数器:逻辑位置计数器和实际位置计数器。其中逻辑位置计数器的输入端接到脉冲发生器的输出端,其功能是计量从脉冲发生器实际发出的脉冲数量。实位计数器的输入端接到编码器的输出端,其功能是计量从编码器发出的脉冲个数。逻辑位置寄存器和实际位置寄存器实际上构成一个闭环系统,前者为闭环系统的输入,后者为闭环系统的输出。当两者的误差范围不超过某一个限度时,在FPGA中对实时的脉冲发送速率进行调节;当两者的误差超过某一个设定的范围时,FPGA 向ARM 发送一个中断请求。当某个轴接收到减速信号SD 或者极限到位信号EL 时,在FPGA 内部经过同样一个中断发生器模块向ARM 发送一个中断。ARM 接收到中断信号后,开启运动控制进程,对PID 控制参数进行整定,计算控制量。

图3 单轴控制模块设计

3.2 驱动程序接口设计

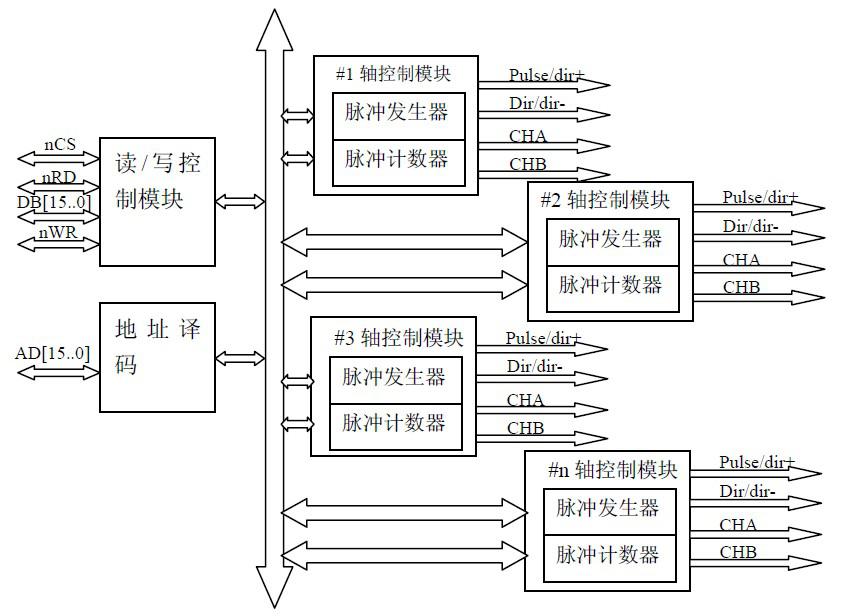

在系统设计中,两片FPGA 作为ARM 的外设,挂在ARM 的外设地址空间。当ARM 要访问FPGA时,首先要在ARM 中运行包含FPGA 所在地址空间地址的指令,而后ARM 的片选线选中FPGA,FPGA检测到自己被选中,从而开始检测地址总线上传来的ARM 指令所包含的地址数据。根据从ARM 地址线传来的地址总线上的数据,FPGA 读取从ARM 数据总线上传来的数据总线上的数据,而后开始进行相应的动作,从而完成一次控制任务。寄存器是本运动控制系统的基本组成部分之一,ARM 对FPGA 的控制就是通过配置在FPGA 内部的寄存器来实现的。完成配置的FPGA 整体结构如图4 所示。

图4 FPGA 内部结构图

4 控制算法设计与仿真

4.1 单神经元自适应PID 控制器设计

单神经元自适应PID 控制器的结构如图5 所示。

图5 单神经元自适应PID 控制器

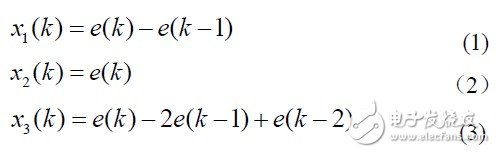

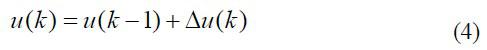

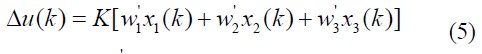

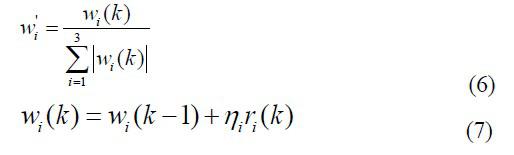

图5 中,神经元的3 个状态变量分别为:

单神经元自适应控制器是通过对加权系数的调整来实现自适应、自学习功能,权系数的调整是根据有监督的Hebb 学习规则实现的。

控制器的输出为:

其中:

式(5)中,w'i为加权系数,可在线修正。加权值的在线学习则采用规范化的学习算法,公式为式(6):

式(7)中ηi(i = I、P、D ), ηI 、ηP 、ηD 分别为积分、比例、微分的学习速率。

4.2 算法仿真

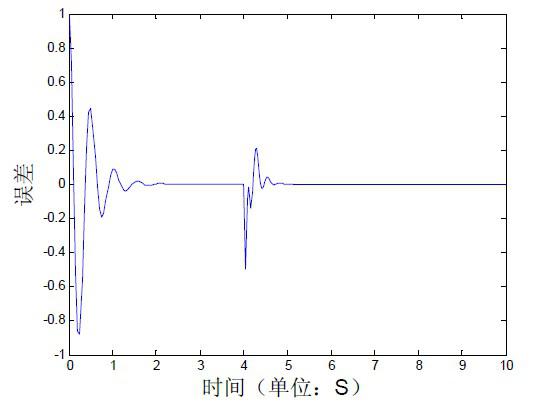

仿真系统的参数:比例、积分、微分的学习速率分别为 ηP =0.40 , ηI =0.35 , ηD =0.40 ,系统初始误差量值设置为1,仿真曲线如图6 所示。从仿真结果可以看出,系统PID 控制参数随系统的运行在线整定,经整定的PID 参数对系统进行控制,系统的误差最终趋于0。

图6 单神经元PID 控制误差曲线

5 运行结果

5.1 系统位移调试结果

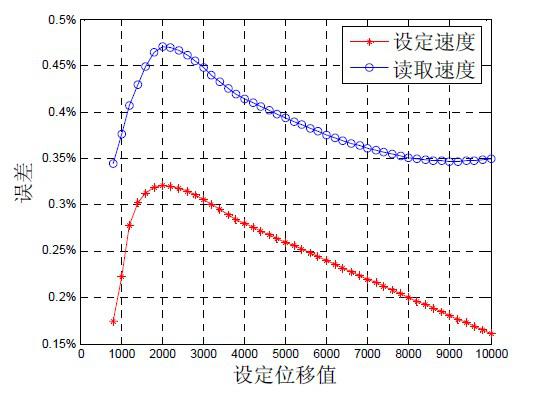

为了测试运动控制系统的位置控制效果,在电机空载时进行了100 次试验,图7 所示为在实验室中测定的电机空载时的位移测试结果曲线图,各试验数据均是取100 次实验数据的平均值。图7 为各实验数据的曲线拟合图。从图中可以看出,电机空载时脉冲发生器和脉冲计数器的误差曲线经历了一个积累的过程,当误差超过设定值0.18%时单神经元自适应PID控制器开始在线整定PID 控制参数,整定结果使系统的误差趋于0。

图7 系统位移调试结果

5.2 系统速度调试结果。

为了测量系统的速度响应结果,系统使用M/T法[7]对速度数据进行测量,M/T 法的计算公式如式(8)所示:

式(8)中f 为基准时钟频率;P 为光电编码器每转一周产生的脉冲个数;M1 和M2 分别是在相同的时间内对编码器脉冲和基准时钟脉冲进行计数的计数值。

在电机空载时进行了100 次试验,图8 所示为在实验室中测定的电机空载时的速度测试结果,各个参数值均是取100 次实验数据的平均值。图8 中设定速度值对应程序运行时在脉冲发生器中设定的分频系数,驱动器显示电机转速对应设定速度时对应的误差,使用M/T 测得的转速对应读取速度时对应的误差。

图8 电机空载时速度测试结果

6 结论

采用嵌入式方案设计的运动控制系统不管在体积、成本还是功能方面,较原有的工控机+板卡的结构均有较大的优势。该系统突破了原有的工业CT 运动控制系统本身固有的一些缺点,采用嵌入式的ARM+FPGA 解决方案进行设计,控制系统内部采用基于单神经元自适应PID 控制器进行设计。系统运行结果证明方案的可行性。为今后进一步研发拥有自主知识产权的基于嵌入式系统的多轴智能运动控制器做了基础性的探索工作。

客服微信

客服微信 查ic网订阅号

查ic网订阅号