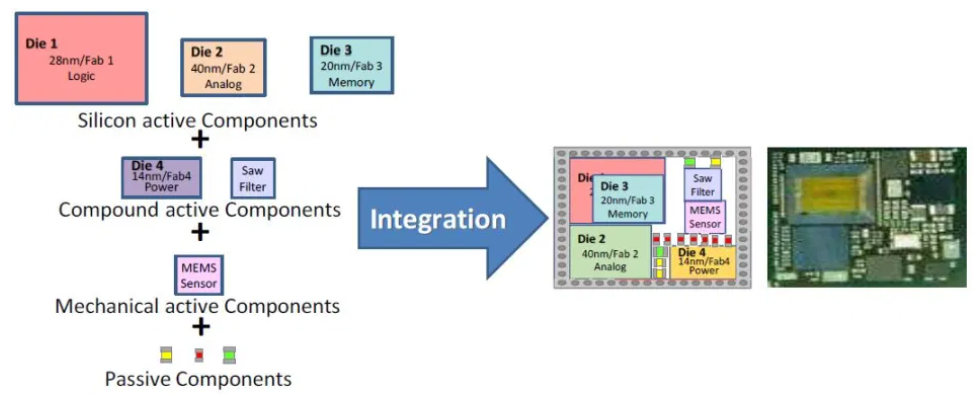

异构集成技术是指将单独制造的组件集成到更高级别的组件或系统封装(SiP)中,总体而言,该组件提供了增强的功能和改进的操作特性。

此外,这类组件可以是任何一种产品,例如微机电系统(MEMS)、高带宽存储器(HBM)的组装封装(例如,无源元件)等(图1)。

图1异构集成技术如何工作的高级视图。

不是摩尔定律的延续

严格地说,摩尔定律是一种观察定律,它要求集成电路中晶体管的密度每两年翻一番。晶体管的集成密度在二维受到限制,这主要是由于栅极长度收缩的减缓,所以才开始使用三位技术。堆叠式内存作为3D晶片就是一个例子,多层相同技术的堆叠,增加了整合密度。

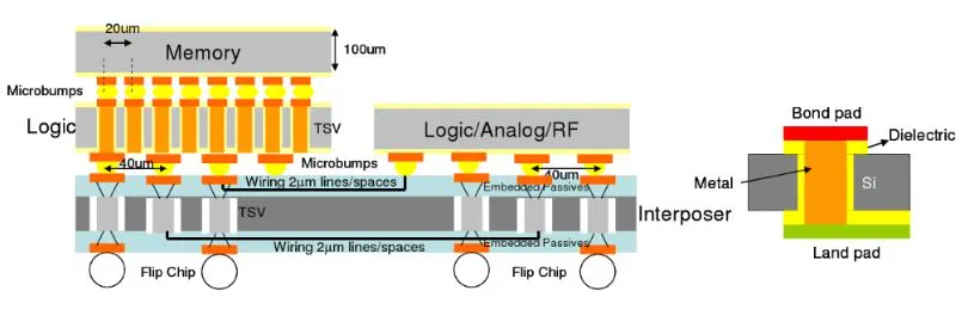

“超越摩尔定律”指的是功能密度的增加,将多种技术集成到一个复合器件中。这可能包括芯片和/或封装的堆叠,使用多种半导体材料和各种电子布线技术,如球栅阵列(BGA)、硅通孔(TSV)、中间层和引线键合。一个超越摩尔的器件可以通过异构集成将来自不同前端制造节点的逻辑、内存、传感器和天线集成到一个单独的封装中。

异构集成不是什么新鲜事

异构集成不是一个全新概念,多芯片组件(MCM)自20世纪70年代开始出现,然而,先进的封装技术使电子封装制造业发生了革命性的变化。新的封装技术使来自不同制造工艺流程的芯片集成到具有多种功能的单个封装中。在过去的二十年里,这些封装技术的多样性在市场需求的推动下正在快速发展,通过更低的成本获得更高的器件性能。

功耗、性能、面积和成本(PPAC)是采用异构集成技术的关键驱动因素。更低的功耗、减少占用空间、更低的延迟、更高的速度和更高的带宽都能为消费者带来优势。

很自然地,扩展仍然是异构集成中的一个考量因素。互连、凸点封装、TSV和焊盘的缩放将有助于提高器件的PPAC。在这一过程中,先进的制程、工具以及方法学带来了更重要的挑战。

光刻技术的转变

光刻也被迫适应先进封装技术的发展。随着设备的复杂性不断发展,设备和封装规模的压力也越来越大,这就导致了许多合作发展机会。由此产生的技术创新需要设备、封装、系统设计师和制造商之间的联合,打破行业部门之间的历史界限。

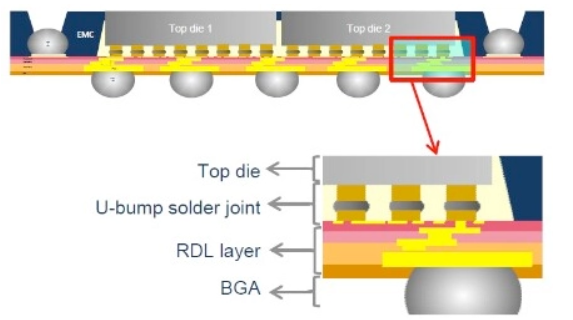

随着异质结构的增加,器件、封装和PCB的融合也将增加,从而产生大量先进的封装解决方案,这些解决方案已经发展到适合特定系统的程度。例如,高性能计算(HPC)应用需要2.5D中间层技术来实现重布线层(RDL)。相比之下,消费者移动和物联网市场要求不那么严格的设计规则,不必采用昂贵的中间层,而是选择使用高密度扇出(HD-FO)封装技术将互连层嵌入到相关模具中。

中间层(TSV)和扇出(TSV-less)技术不是互斥的,可以组合在一个单一的混合技术封装中,最终很大程度上取决于器件的需求。

引线互联有两个方案。传统上,金属化互连被认为是一个BEOL领域,但随着2.5D和3D架构的出现,这一界限变得模糊。对高性能互连的要求,要求垂直的连接TSV或TMV,直接通过硅,补充和取代传统的线连接和倒装芯片解决方案,过孔技术已成为实现高性能互连的关键(图2)。

图2异构集成展示了TSV和中间层功能。

RDL和bumping挑战

随着互连技术的变化,生产它的光刻技术要求也随之改变。一些以前的BEOL过程现在使用FEOL工具运行,而一些BEOL工具现在在运行BEOL晶圆时按照FEOL标准执行。所有的光刻工艺都强调特征分辨率、临界尺寸(CD)控制和覆盖精度指标,同时保持高生产率和低成本。

由于分辨率的原因,通常在高数值孔径(NA)下操作的FEOL光刻工具现在的任务是精细线/空间、通孔和微凸图形,以实现初始互连定义。随着互连层和再分配层的密度增加,与较厚的光刻胶膜、基板翘曲和聚焦深度相关的挑战变得复杂,频繁出现在FEOL上的高钠光刻系统不再能够满足困难制程。

某些先进的封装技术采用更为困难的工艺流程,从而导致更难制造晶圆。例如,在无TSV重组eWLB或扇出型晶圆上的模具移位和晶圆形貌,这分别对高级封装光刻工艺流程中的覆盖和聚焦深度造成挑战。这是一个不同的光刻方法是需要的,利用BEOL光刻工具,已经开发了解决这些问题的实用且通用的解决方案。

其次,倒装芯片(bumping)是一个定义明确且稳定的过程,多年来一直是行业标准。尽管它也受到了扩展的影响,但bumping仍然是异构集成的高级打包的基础。一般来说,凸点光刻是用较厚的感光材料进行的,这些材料受益于具有低钠和高聚焦深度的模具,以定义更大的倒装芯片。

这是一个多芯片的概念性实现,带有微凸点、铜柱和倒装芯片凸点,在这种情况下不需要TSV,使用Amkor的硅片集成扇出技术(SWIFT)。

然而,随着行业细分的缩小,将FEOL和BEOL拉近,BEOL工具的灵活性变得至关重要。处理翘曲晶圆的能力、宽频曝光GHI、多膜堆的GH和I线波长,以及具有大深度聚焦控制的分辨率适应性的可变NA,这些都被证明对高生产率、高产量和良好的成本至关重要。

这种灵活性将是极其重要的,特别是外包半导体封装厂(OSAT)。与各种FEOL曝光场尺寸、衬底尺寸和材料类型相匹配的多功能性也是一个重要的考虑因素。提高精度以实现更紧密的覆盖、更高的生产效率和更高的曝光均匀性以改善CD均匀性,这一要求将FEOL和BEOL工具性能结合起来,用于前沿的异质集成技术应用。

现代前沿应用,如人工智能(AI)、高性能计算机(HPC)、5G、物联网(IoT)和移动消费品,正以越来越低的成本推动对电子设备性能的需求。异质集成技术使半导体器件制造商能够将来自不同制造工艺流程的功能部件组合成具有复杂和先进功能的单一复合器件。

由这些技术产生的先进封装生产需求对光刻和补充工艺提出了挑战,要求它们以更高的标准执行,以支持所需的互连和TSV处理层要求。在这里,设备成本和由于复杂性增加而降低的生产率或产量是制造商将要解决的挑战。在产量和工艺流程的进步之前,高端应用将从异构集成中获益。

客服微信

客服微信 查ic网订阅号

查ic网订阅号