从许多方面讲,Pipelines是一种加快任务处理速度的通用方法,因此有可能在制造业或日常生活中(例如洗衣服或做饭)找到无数类似的东西。

从本质上讲,我们都面临着在每个时间单位上完成尽可能多的工作的挑战。有很多方法可以实现这一目标。我将通过不同的方法来帮助您了解微处理器设计人员如何将流水线作为一种智能解决方案。我们将看:

时钟频率。早期的CPU如何通过增加时钟频率来提高速度。

并行执行。如果您不能更快地执行指令,那么如何并行执行更多指令?

流水线适用于无法并行执行更多任务且无法小型化以增加时钟频率的情况。

通过增加时钟频率来加速CPU

计算机在离散时间执行的工作,称为时钟周期。在一个时钟周期内,最小的任务在CPU中执行。这有点像机械表仅在齿轮上的齿轮移动一个步骤时才会执行某些操作。两者之间什么都没有发生。

提高微处理器性能的最直接方法是缩短一个时钟周期的长度。但是,时钟周期的缩短是有限制的。您不能使电子运动更快。它们必须能够移动CPU中所有必需的晶体管,以完成一个时钟周期内应该执行的操作。

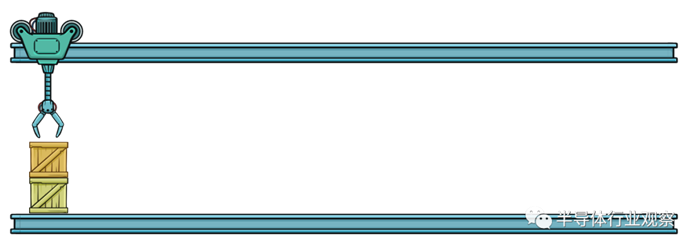

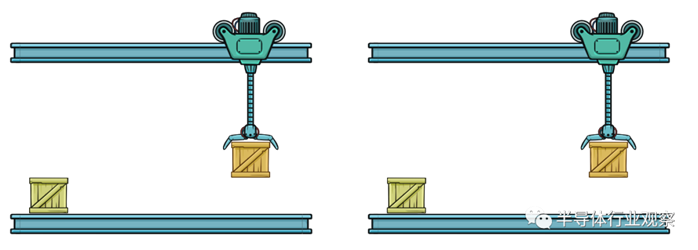

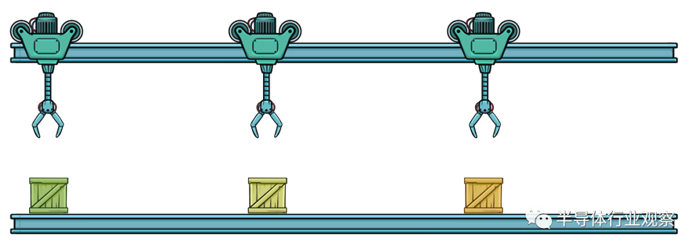

用仓库机器人的类比更容易弄清楚。我们在仓库中配备了一个机器人,负责在一端拣选包裹并在另一端交付包裹。

可以说这个机器人也有一个时钟周期。时钟周期是机器人在最后交付包裹并返回到开始所花费的时间。这意味着移动包裹的任务已经完成。用CPU来说,这是完成一条指令所花费的时间。

仓库机器人正忙着将橙色包装移到生产线的尽头。

就像电子一样,我们必须想象不可能加快机器人的速度。如果我们使时钟周期太短,则机器人将没有时间交付包裹并返回分配的时间。

想象一下,机器人仅回到一半位置,然后您指示它拾取包裹并交付。除非它不能装箱,因为它不在起始位置。

小型CPU的好处

如果我们不能使机器人运动更快,该如何在更少的时间内完成工作?用CPU术语来说,那就是是:如果我们不能使电子运动更快,我们将如何使它们更快地到达目的地?

简单的答案是使微处理器更小。在仓库类比中,这意味着缩短机器人必须行进的距离。本质上,我们正在重组仓库以使其更紧凑。我们将其小型化。现在,机器人可以在更短的时间内来回移动,从而缩短了每个时钟周期。

如果距离较短,则可以更快地执行移动任务。

较短的时钟周期与较高的时钟频率相同。因此,使电子设备小型化是提高时钟频率并完成更多工作的一种方法。

并行执行

但是我们有多少可以使微处理器小型化。因此,CPU设计人员的下一步是并行执行更多操作。但是,有许多方法可以实现并行化。让我们看一些策略。

向量处理

早期的超级计算机(例如Cray-1)使用矢量处理器。在这种情况下,我们尝试通过并行处理数据来做更多的事情。这意味着一次只执行一条指令,但是同时对多个数据元素执行该指令。仓库的比喻是让机器人在每次运行中都拾取多个包裹。

同时移动多个数据包对应于对多个数据同时执行相同的操作。这就是我们所说的向量处理。

多个微处理器内核

另一个选择是实际并行执行多个指令。那就是我们今天所说的多核CPU。用仓库的比喻是让两个或多个机器人并行工作。

在多核处理器中,并行执行多个指令。原则上,每个仓库机器人可以彼此独立地工作。

流水线

现在我们终于开始谈流水线了。如果无法缩小微处理器尺寸了怎么办?用仓库的术语来说,这意味着您不能缩短与需要运送包裹(数据)的目的地的距离。我们认为将包移动作为执行指令。

我们移动的长度与电子必须穿过晶体管的距离有关。在这方面,小型化是有帮助的。但这也与指令的复杂程度有关。指令越多,电子必须通过的晶体管越多。

因此,我们可以将指令复杂性视为延长电子必须行进路径的某种方式。如果我们不缩小CPU本身,而是减少每条指令的复杂度怎么办?如果我们使每条指令更简单,那么电流就必须流经更少的晶体管。一种方法是将一条指令分成多个较小的步骤。

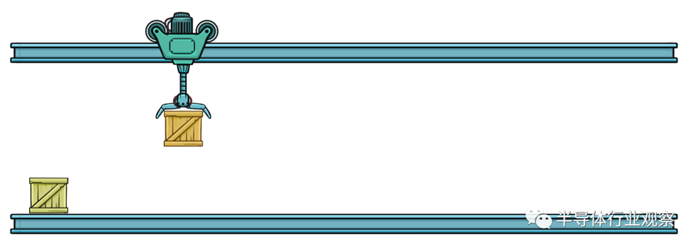

将包裹的移动分为三个单独的步骤。每个机器人只携带包裹的1/3。

时钟周期——1

在我们的仓库类比中,这相当于在同一条生产线上添加更多的机器人,并让每个机器人只移动包裹的一部分。请注意,这与并行化有什么不同,在并行化中,我们添加了完全独立的行,使机器人可以彼此独立地移动。

当“流水线”被填满时,另外两个仓库机器人必须首先保持空闲状态。第一个机器人将橙色包装移动了1/3。这是第一个时钟周期。

在这种情况下,发生的情况是第一个机器人没有一直移动到最后。而是在返回之前,它会移动更短的距离并从包装中掉落。记住,我们将时钟周期视为每个机器人移动包裹并返回下一个包裹所花费的时间。这意味着通过这种设置,我们可以减少一个时钟周期的长度,这相当于增加时钟频率的能力。

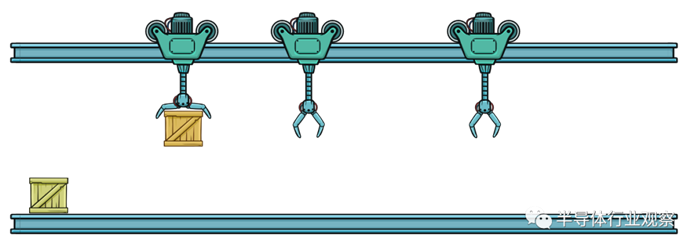

第一个时钟周期已完成。第二个机器人尚未准备好拿起橙色包装并将其移动到最终目的地的2 / 3rd。

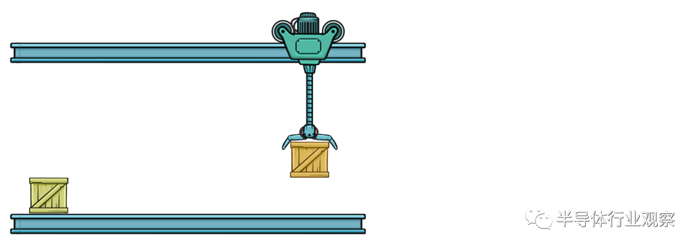

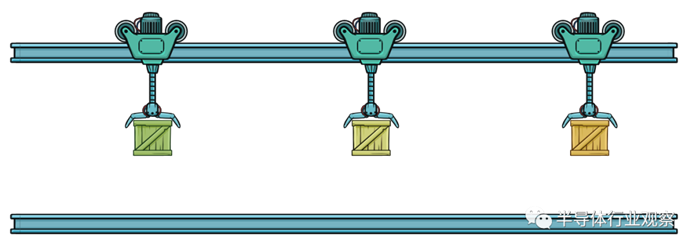

时钟周期——2

在第二个时钟周期,第二个机械手能够开始移动橙色包装,而第一个机械手开始拾取并移动黄色包装。另请注意,仓库人员正在携带新包装,绿色包装。

第一仓库机器人和第二仓库机器人现在可以并行移动包裹。但是他们必须严格执行此操作以避免冲突。这是第二个时钟周期。

当第二个时钟周期结束时,橙色包装可用于第三个机器人的拾取。第二个机器人同时可以拾取黄色包装。第一个机器人可以提取新的绿色包装。

第二个时钟周期结束。整个“流水线”现在已满。在下一个时钟周期,所有三个机器人都可以并行工作。

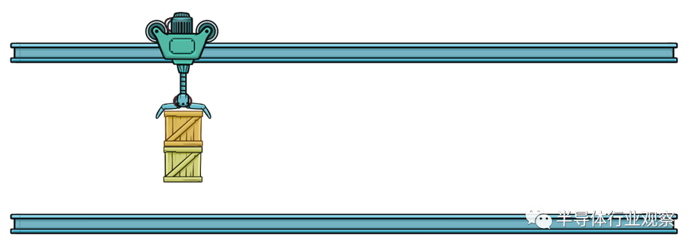

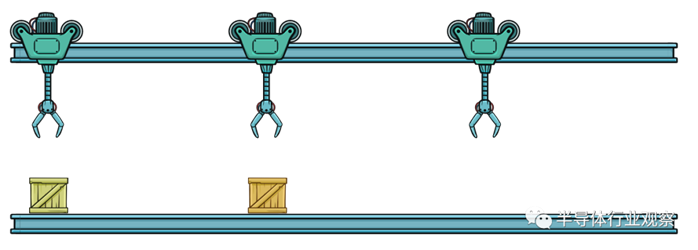

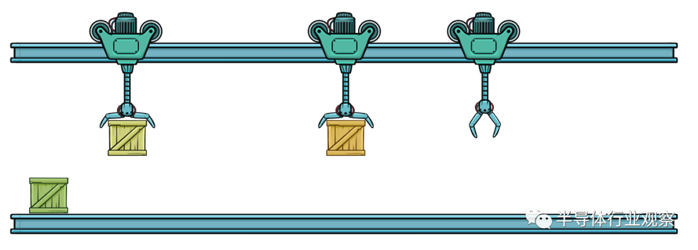

时钟周期——3

在第三个时钟周期,所有机器人都同步移动,进一步移动其包裹。值得反思一下这里发生的事情。程序包从头到尾移动所需的时间并没有真正改变。想象一下,用一个机器人花了30秒将包裹一直移动到最后。现在将包装移动一个步骤,需要10秒钟,但是我们需要树形步骤,因此总时间是相同的。

三个机器人均按步调移动包裹。“流水线”已满,这是最有效的时间,因为每个时钟周期我们都在末尾交付一个包裹并选择一个新的包裹。

那么,我们在这里获得了什么呢?这样做的好处是,每隔10秒钟便会在最后一次交付新包裹,因为我们一直在保持包裹的飞行状态。我们让新包裹从一开始就坐着,等待较短的时间,然后机器人将它们拿起。

流水线的优点和挑战

我们可以用计算机科学中的两个重要概念来描述这一点:

延迟

从操作开始到完成所花费的时间。例如,这可能是您首次提出要求之后收到网络软件包所花费的时间。在我们的案例中,我们可以将其视为执行开始后完成一条CPU指令的延迟。

吞吐量

是我们每个时间单位可以处理多少数据,指令或其他内容。在仓库中,这是每分钟交付的包裹数,例如,对于我们的CPU,这是我们每个时钟周期平均完成多少条指令。

由于我们每10秒钟推出一个包裹,而之前却花费30秒钟,因此吞吐量得到了提高。通过并行化操作,我们还可以提高吞吐量。但是,这并不总是可能的。但这基本上就是图形卡CPU获得出色性能的方式。他们没有做每个单独的操作那么快。换句话说,延迟不一定很大。但是,它们并行执行大量任务,从而导致大量吞吐量。

但是对于通用CPU,通常无法进行大规模瘫痪。因此,流水线很重要。但是正如我们在仓库示例中看到的那样,要使此机器人正常工作,每个机器人需要移动大约相同的长度。否则,它们将无法同步移动。因此,将CPU指令拆分为多个相等长度的步骤非常重要。

RISC与CISC微处理器

这就是为什么在1990年代Unix工作站中使用早期RISC处理器(例如MIPS和SPARC处理器)的原因,其速度要比x86处理器快得多。x86处理器是CISC处理器。从未考虑流水线设计的CISC处理器。但是,RISC设计师考虑到了这一点。精心设计的RISC指令全部分为4个逻辑步骤。这样就可以建立一个4步深的流水线。因此,RISC指令将需要4个时钟周期来执行,但是每个时钟周期中,一条指令将完成执行。

英特尔意识到,他们必须找到一种方法来流化其可变长度的复杂指令。因此,他们提出了微操作。他们会将复杂的指令分解为多个微操作,然后在这些微操作中将其简单化,以馈入管道。

流水线过长

因此,英特尔开始将他们的指令分成越来越小的部分,这使他们可以大大提高时钟频率。因此,例如奔腾4是时钟频率的野兽。这使得英特尔处理器上的流水线真的很长。

在这里,我们碰到了一个我还没有介绍的东西:分支。您会看到指令并不是作为一种无尽的可预测线性流来的。真正的程序可以做出决定和重复。一遍又一遍地重复一些指令。不同类型的数据需要由不同的指令处理。因此,在实际程序中存在条件跳转。检查条件,然后基于该条件,CPU跳转代码。

对于流水线来说这是一个问题吗?想象一下,您有一个非常深入的流水线,其中有100条指令正在运行。您可以直观地看到这一点,因为我们有100个仓库机器人排成一行地排成一行地移动了100个包裹。最后一条完成的指令是条件跳转指令。根据该指令的结果,CPU可能会意识到当前正在流水线中的所有这100条指令实际上不是要执行的正确指令。我们应该在内存中的其他地方拾取完全不同的指令。

因此,必须刷新整个流水线,并且我们必须等待整个100个时钟周期,然后另一条指令会通过流水线到达最后。这对性能有很大的影响。

这就是为什么苹果公司有一张幻灯片比较基于RISC的PowerPC芯片的原因,直到2006年,他们才使用Mac和Intel的Pentium处理器。奔腾处理器具有更高的时钟频率,但流水线也更长。那时人们认为时钟频率等同于性能。正如我们所看到的,它显然是相关的,但并不完全相同。

奔腾处理器的超长流水线会经常被冲洗掉,从而严重影响性能。同时,PowerPC芯片的时钟频率较低,但流水线更短,从而导致条件跳转对性能的影响小得多。

从那以后我们通过利用分支预测变量来减少这个问题是毫无价值的。这意味着在实际执行测试条件的指令之前猜测分支会去哪里。

客服微信

客服微信 查ic网订阅号

查ic网订阅号