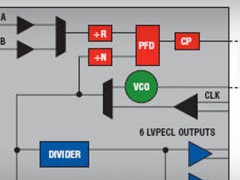

ADI:大型多GHz时钟树中的相位偏差

本文指出了设计过程、制造过程和应用环境中可能导致1 ps或以上相位偏差的几个关切问题。对于这些关切问题,本文将提供一些建议、示例和经验法则,帮助读者直观地了解相位偏差的根本原因和幅度。

2020-04-26 15:43:11所有功能AEC-Q100 grade 0 conform qualificationCompatible with the serial peripheral interface (SPI) busMemory array4 Mb

2021-09-01 10:09:40所有功能AEC-Q100 grade 0 conform qualificationCompatible with the serial peripheral interface (SPI) busMemory array4 Mb

2021-09-01 10:09:34所有功能AEC-Q100 grade 0 conform qualificationCompatible with the serial peripheral interface (SPI) busMemory array 4 M

2021-06-01 14:10:07所有功能AEC-Q100 grade 0 conform qualificationCompatible with the serial peripheral interface (SPI) busMemory array 4 M

2021-06-01 14:10:06Silicon Labs在其经AEC-Q100认证的Si5332-AM时钟发生器系列中引入了SmartClock功能,旨在扩展基于硅的汽车定时解决方案。新的Sma

2021-01-26 14:02:24

本文指出了设计过程、制造过程和应用环境中可能导致1 ps或以上相位偏差的几个关切问题。对于这些关切问题,本文将提供一些建议、示例和经验法则,帮助读者直观地了解相位偏差的根本原因和幅度。

2020-04-26 15:43:11

A discussion around time jitter and a solution to some of the challenges it creates.

2020-04-26 15:19:43

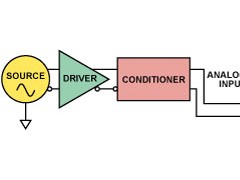

A discussion of how high-speed amplifiers can be less expensive than traditional clock buffers in consumer electronic applications.

2020-04-26 15:17:06

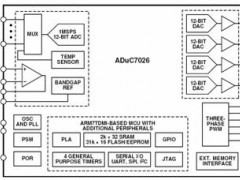

A look at three methods for generating a clock using an ADuC702x Analog Microcontroller.

2020-04-26 15:15:55

Is an analog-to-digital converter encode circuit with a respectable 350 femtoseconds (fs) of jitter adequate for today’s high speed requirements?

2020-04-26 15:15:24